# Design and Verification of USB 3.0 Link Layer (LTSSM)

Rohit Kumar School of information Sciences Manipal University Manipal, India Hardik Trivedi School of information Sciences Manipal University Manipal, India Nitish Alok School of information Sciences Manipal University Manipal, India

Abstract-In this proposed design it mainly includes USB 3.0, LTSSM. The Link Training and Status State Machine (LTSSM) have downstream and upstream ports. Transitions of all 12 link states and their subs -states of both downstream and upstream have been designed. The proposed model is implemented using Verilog HDL. Proposed model in this paper has been verified using SystemVerilog.

#### **1.** INTRODUCTION

USB is an industry standard developed in the mid-1990s, it defines the cables, connectors and protocols used in a bus for connection and communication between computers and electronic devices. The first USB technology began development in 1994, co-invented by Ajay Bhatt of Intel and the USB-IF (USB Implementers Forum, Inc).

Before USB came into existence, computers used serial and parallel ports to plug devices into computers and transfer data. Expansion cards and custom drivers were often required to connect the devices. Parallel ports transferred data at approximately 100 kilobytes per second, where as serial ports ranged from 115 to more than 450 kilobits per second. The high extent of incompatibilities and the attempt to use multiple interfaces helped in the growth for a technology like USB. Immediate interaction between devices and a host computer without the need to disconnect or restart the computer also enables USB technology to furnish more efficient operation. Consequently, a single USB port can handle up to 127 devices while offering a collective compatibility.

Versions of USB specification:

- Revision 1.0 released on January 15, 1996, introduced a low-speed transfer rate of 1.5 Mbit/s and a full-speed transfer rate of 12 Mbit/s.

- Revision 1.1 released on September 23, 1998, introduced the improved specification and was the first widely used version of USB.

- Revision 2.0 released on April 27, 2000. The major feature of revision 2.0 was the addition of a high-speed transfer rate of 480 Mbit/s.

- Revision 3.0 released on November 17, 2008, brings significant performance enhancements to the USB standard while offering backward compatibility with the peripheral devices currently in use. Delivering data transfer rates up to ten times faster (the raw throughput is up to 5.0 Gbit/s) than Hi-Speed USB (USB 2.0).

#### 2. USB 3.0 LINK LAYER

Link Layer helps in traffic management between the two links connected to each other. It manages the port to port flow of data between the host and the device.

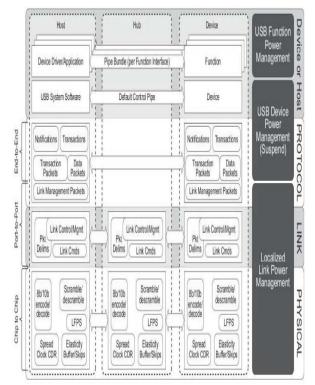

Fig 1: USB Layout Diagram [1]

The Link Layer functions consist of:

- Effective power management for 4 link power state (U0, U1, U2, and U3).

- Packet and link command formation.

- Link training symbol lock and Rx-equalization.

- Packet header formation.

- Different types of error handling.

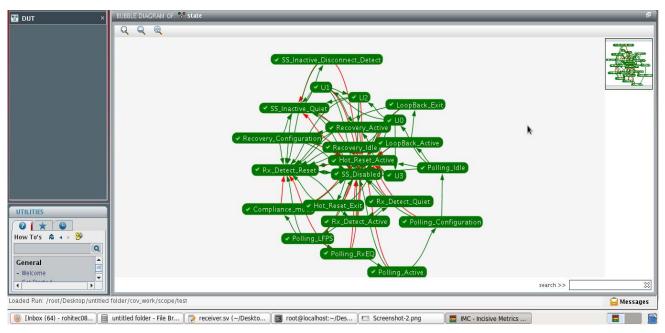

#### **3.** USB **3.0** LTSSM

LTSSM (Link Training and Status State Machine) is the state machine used for link connectivity and link power management. LTSSM consist of 12 main link states and their sub-states. These states and sub-states are responsible for link training, power management and error testing.

Fig 2: State diagram of LTSSM [1]

## 4. USB 3.0 LTSSM STATE DESIGN

The proposed USB3.0 LTSSM architecture is consisting of following states and their sub-states:

#### 4.1 SS.Disabled

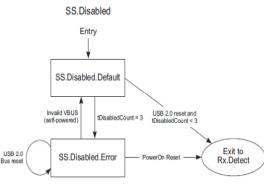

It is a state where a port's SuperSpeed connectivity is disabled. It does not contain any sub-states in case of downstream port and hub upstream port but contain two sub-states for peripheral upstream port.

- SS.Disable.Default

- SS.Disable.Error

Fig 3: SS.Disabled Sub-state Machine [1]

#### 4.2 SS.Inactive

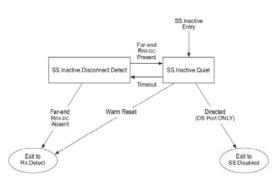

It is a state where a link has failed SuperSpeed operation and USB is non-operable. It contains two sub-states:

- SS.Inactive.Disconnect.Detect

- SS.Inactive.Quiet

Fig 4: SS.Inactive Sub-state Machine [1]

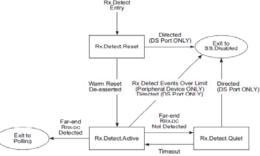

#### 4.3 Rx.Detect

It is the initial state after reset, called as power on state of LTSSM for both downstream port and upstream port. It detects the presence or absence of a device connected at far end of the link. It contains three sub-states:

- Rx.Detect.Reset

- Rx.Detect.Active

- Rx.Detect.Quiet

Fig 5: Rx.Detect Sub-state Machine [1]

### 4.4 Polling

It is a state where link training starts. It contains five substates:

- Polling.LFPS

- Polling.RxEQ

- Polling.Active

- Polling.Configuration

Fig 6: Polling Sub-state Machine [1]

## 4.5 Compliance Mode

It is used to test the transmitter as per given voltage and timing specification. It does not contain any sub-state.

# 4.6 U0

It is normal power state and does not conation any sub-state.

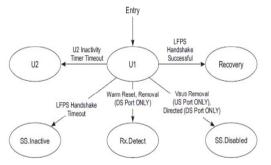

# 4.7 U1

It is low power state where no transmission of packets is done.

Fig 7: Transition to other state from U1 [1]

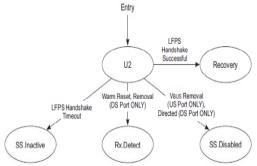

## 4.8 U2

It is even low power state than U1 but exit latency increased in this state.

Fig 8: Transition to other state from U2 [1]

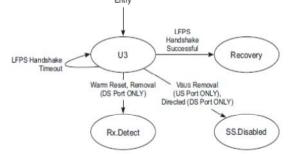

# 4.9 U3

It is lowest power state, where device is put into a suspend state.

Fig 9: Transition to other state from U3 [1]

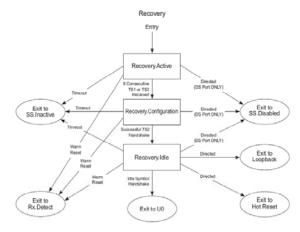

#### 4.10 Recovery

Retraining of the link is done in this state. It contains three substates:

- Recovery.Active

- Recovery.Configuration

- Recovery.Idle

Fig 10: Recovery Sub-state machine [1]

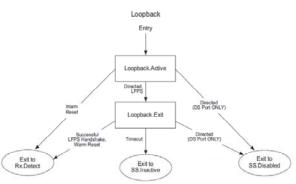

#### 4.11 Loopback

It is used as test and fault isolation state. It contains two substates:

- Loopback.Active

- Loopback.Exit

Fig 11: Loopback Sub-state machine [1]

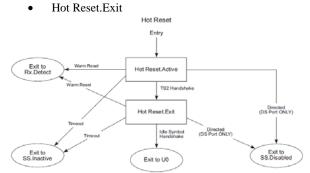

#### 4.12 Hot Reset

This state is entered when it is directed to do so by a device's higher layer. It contains two sub-states:

Hot Reset.Active

Fig 12: Hot Reset Sub-state machine [1]

#### 5. VERIFICATION

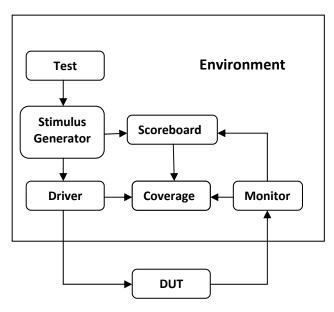

The verification of above LTSSM design for Upstream port is carried out to check that if all the states and sub-states are covered or not. There are 18 different signal which drives LTSSM. All 18 different signals have been given as input to design and respected state has been monitored. These states have been assigned as output. Verification is done using SystemVerilog.

Fig 13: Test Bench Architecture

#### 5.1 Interface

It consists of bundle of signals which can be referenced throughout a design to simplify hierarchical connections and module instantiation i.e. used to connect the testbench to the DUT.

## 5.2 Stimulus

Using SystemVerilog randomization, stimulus is generated automatically. SystemVerilog high-level data structures helps in storing and processing of stimulus in an efficient way.

# 5.3 Stimulus Generator

It generates stimulus which are sent to DUT by driver. Randomization of stimulus has been done in this block. Automatic randomization didn't cover all the states of LTSSM, so some directed random testcases is written here. Mailbox sg2dr is created to send the generated stimulus to the driver block.

# 5.4 Driver

It repeatedly receives a data items from mailbox sg2dr and drives it to DUT by sampling and driving the DUT signals. The driver also sends the stimulus to scoreboard using drv2sb mailbox.

# 5.5 Monitor

This block receives the output of the DUT i.e. output of LTSSM design. The output is sent to the scoreboard using mailbox rcv2sb.

#### 5.6 Scoreboard

This block receives the stimulus from the driver through the mailbox drv2sb and also receives the DUT output from monitor through the mailbox rcv2sb. In LTSSM design, for different stimulus there will be different states, so in scoreboard expected state for all the combination of stimulus has been written and compared with DUT output receives from mailbox rcv2sb. If it matches then LTSSM design is working correctly.

#### 5.7 Environment

It contains the instances of the entire verification component

Methods defined in Environment class:-

- <u>build()</u>: all the objects like driver, monitor etc are constructed.

- reset(): reset the DUT.

- start(): To call the methods which are declared in the other components like driver and monitor.

- <u>run()</u>: This method calls all the above declared methods in a sequence order.

- <u>Report</u>): Its main function is to detect the errors in the design and report the errors.

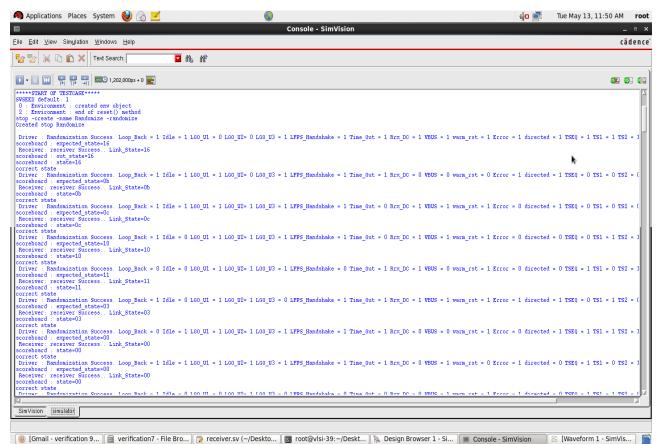

#### **6.** SIMULATION RESULT

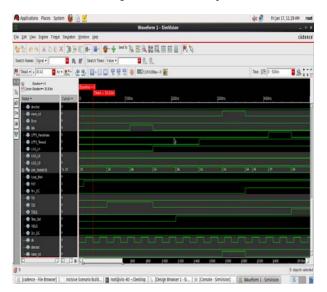

The output Link\_state changes with change in the input signal.

LTSSM design for Downstream port

Fig 14: Downstream port simulation

#### LTSSM design for Upstream port

LTSSM design for upstream port consists of SS.Disabled substates.

|| New folder123... 🗇 (project\_thu /K... | 👔 (notifylsi-42/... | ). (Design Browne... | III (Conside - Sim... ) 👸 Waveform 1 - S... || (project\_new1 - ... | = (Screenbact.proj) ) 🐻 🎆

Fig 15: Upstream port simulation

# 7. VERIFICATION RESULT

# 7.1 Scoreboard

Fig 16: Scoreboard

# 7.2 Coverage Report

|                               |                                    |                      | IMC - Inc    | isive Metrics Cen    | ter [test]    |                       |                                    |                     | _ C                  |

|-------------------------------|------------------------------------|----------------------|--------------|----------------------|---------------|-----------------------|------------------------------------|---------------------|----------------------|

| e View Help                   |                                    |                      |              |                      |               |                       |                                    |                     | cāder                |

| T                             | 🗵 Summary 🛛 🛃 Load 👻               | 💿 All Metrics \      | view 🔹 📔 🏻   | vnalyze , Lookup     | - Layout - R  | efinement 🝷   🧇 🖒     |                                    |                     |                      |

| NAVIGATION                    | VERIFICATION HIERARCHY             |                      |              |                      |               | • • •                 | INFO TABS OF: 📴 Verification       | Metrics             |                      |

| Summary                       | Ex Name                            | Local                | Local        | Local                | Overall Grade | Overal Overall C      | 🔄 Sub Elements                     |                     |                      |

|                               | - Verification Metrics             | Overall Grade<br>n/a | Overall Unco | vere Overall Covered | 91.3%         | Uncov<br>2584698 / 26 | Recursive                          |                     | 0                    |

|                               | E C Types                          | n/a                  | 0            | 0/0                  | 91.77%        | 1292345 / 13          | Ex Name C                          | verall Grade Overa  | all Overall          |

|                               | G Instances                        | n/a                  | 0            | 0/0                  | 90.84%        | 1292353 / 13          |                                    |                     | vered Covered        |

|                               | 1 \$unit_0x47e4bf35                |                      | 129086       | 2020 / 131106        | 94.53%        | 1292020 / 13          | (no filter)                        | (no filter) (no fi  |                      |

|                               |                                    | 100%                 | 0            | 3/3                  | 87.15%        | 72 333 / 405          |                                    | 91.77% 1291         |                      |

|                               | I inp                              | n/a                  | 0            | 0/0                  | n/a           | 0 0/0                 | nstances [                         | 90.84% 1291         | 58 2353/1            |

|                               | I out                              | n/a                  | ő            | 0/0                  | n/a           | 0 0/0                 |                                    |                     |                      |

|                               | TC                                 | 75%                  | 1            | 3/4                  | 75%           | 1 3/4                 |                                    |                     |                      |

|                               |                                    | 89.31%               | 65           | 305/370              | 86.44%        | 71 327 / 398          |                                    |                     |                      |

|                               |                                    |                      | 05           | 5057570              | 00.44%        | 12 5277 550           | Showing 2 items                    |                     |                      |

|                               |                                    |                      |              |                      |               |                       | DETAILS OF: 🖪 Verification Metrics |                     |                      |

|                               |                                    |                      |              |                      |               |                       | Metrics Attributes Source          |                     |                      |

|                               |                                    |                      |              |                      |               |                       |                                    |                     |                      |

|                               |                                    |                      |              |                      |               |                       | Ex Name                            | Local<br>Overall Cr | Overall<br>ade Grade |

|                               |                                    |                      |              |                      |               |                       | 🗆 🔇 Overall                        | n/a                 | 91.                  |

|                               |                                    |                      |              |                      |               |                       | 🗄 🌍 Code                           | n/a                 | <b>E</b> 89.         |

|                               |                                    |                      |              |                      |               |                       | Block                              | n/a                 | <b>86</b> .          |

|                               |                                    |                      |              |                      |               |                       | — Expression                       | n/a                 | 10                   |

|                               |                                    |                      |              |                      |               |                       | O Toggle                           | n/a                 | <b>1</b> 00          |

| TILITIES                      |                                    |                      |              |                      |               |                       | SM ESM                             | n/a                 | 84.                  |

|                               |                                    |                      |              |                      |               |                       | 🖃 🌖 Functional                     | n/a                 | 94.                  |

|                               |                                    |                      |              |                      |               |                       | Assertion                          | n/a                 | n/a                  |

| w To's 🚔 🛪 🕨 🌽                |                                    |                      |              |                      |               |                       | OverGroup                          | n/a                 | 94.                  |

| Q                             |                                    |                      |              |                      |               |                       |                                    |                     |                      |

|                               |                                    |                      |              |                      |               |                       |                                    |                     |                      |

| eneral 🍨                      | × Q Name                           | <b>~</b> ~           | -            |                      |               | <b>₩</b>              |                                    |                     |                      |

| ·····                         | Showing 9 items                    | • •                  | •            |                      |               |                       | Showing 9 items                    |                     |                      |

| ad Pup: /modia/HP.v230w/rosu  | t/untitled folder/cov_work/scope/t | tost                 |              |                      |               |                       | P                                  |                     | 0                    |

| ieu kun, /meura/mr vzzow/resu | in/unitied folder/cov_work/scope/i | lesi                 |              |                      |               |                       |                                    |                     | 🔒 Messa              |

Fig 17: Coverage result

Fig 18: Full FSM coverage report

#### 8. CONCLUSION

This design explains the concept of USB 3.0 LTSSM and their different states and sub-states. Since the data received by scoreboard same as the expected state of the design, therefore proposed design of LTSSM is functionally correct. As shown in figure 16 states are correctly matched. Figure 17 shows the different types of coverage report of the design i.e. toggle coverage, expression coverage, and functional coverage and toggle coverage. Figure 18 shows that all the states of proposed design is successfully covered.

#### **9.** ACKNOWLEDGMENTS

We would like to thank our professors Mr. Sunderasan C. and Asst. Prof Samarendranath Bhattacharya for being our advisor and guide. We are grateful to them for their continuous support and help throughout the development of the project. We would also like to thank our friends Ashwin K Rao and Ronak Tank who helped us during this project.

Besides, we would like to thank our department School Of Information Science for providing us with a good environment and facilities to complete this project. At last but not least gratitude goes to all of my friends who directly or indirectly helped me to complete this project.

#### REFERENCES

- [1] "Universal Serial Bus 3.0 Specification", Revision 1.0, November 12, 2008.

- [2] "Universal Serial Bus 2.0 Specification", Revision 1.0, March 13, 2006.

- [3] PCI Express Base Specification, Revision 2.0, December 2006

- [4] M. Aguilar, A. Veloz and M. Guzman, "Proposal of implementation of the" data link layer" of PCI-express", Proceedings of 1st International Conference on Electrical and Electronics Engineering, pp. 64, June 2004.

- [5] Ravi Budruk, Don Anderson & Tom Sanely, 2004. "PCI Express System Architecture", Mindshare Inc., pp 419-434.

- [6] Chris Spears, "System Verilog for Design, "A Guide to Using System Verilog for Hardware Design and Modeling," Springer Second edition.

- [7] http://www.mindshare.com/files/resources/MindShare\_Intro\_ to\_USB\_3.0.pdf.

- [8] Verilog HDL by Sameer Palnitkar.